The article is from https://support.xilinx.com/s/article/1053914?language=en_US

TITLE

AXI Basics 1 - Introduction to AXI

AUTHOR

florentw

LAST PUBLISHED DATE

10/13/2021, 7:26 AM

BODY

Introduction

These days, nearly every Xilinx IP uses an AXI Interface. Zynq® , Zynq MP, MicroBlaze™ and the new Versal™ Processors all use AXI interfaces. Thus AXI interfaces are part of nearly any new design on Xilinx devices. Understanding the basics of it can be useful to design and debug designs on Xilinx devices.

This blog entry will cover some of the basics of AXI3/AXI4 on Xilinx devices. First we will start with the less exciting parts, the theory and the terminology.

What is AXI?

AXI, which means Advanced eXtensible Interface, is an interface protocol defined by ARM as par of the AMBA (Advanced Microcontroller Bus Architecture) standard.

The AXI3/AXI4 specification are freely-available on the ARM website (link) so I encourage anybody who is interested to download it.

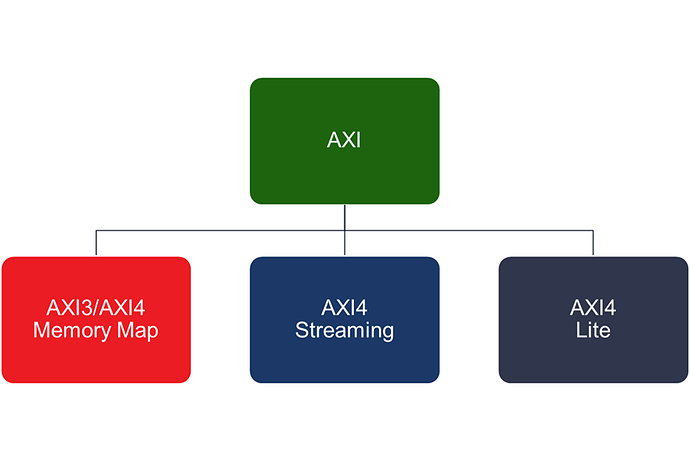

There are 3 types of AXI4-Interfaces (AMBA 4.0):

- AXI4 (Full AXI4): For high-performance memory-mapped requirements.

- AXI4-Lite: For simple, low-throughput memory-mapped communication (for example, to and from control and status registers).

- AXI4-Stream: For high-speed streaming data.

- Note: AXI4-Stream is not covered in this entry. “AXI” here will refer to AXI3, AXI4 and AXI4-Lite.

Note: The AXI3 Interface is close to the full AXI interface.

AXI Read and Write Channels

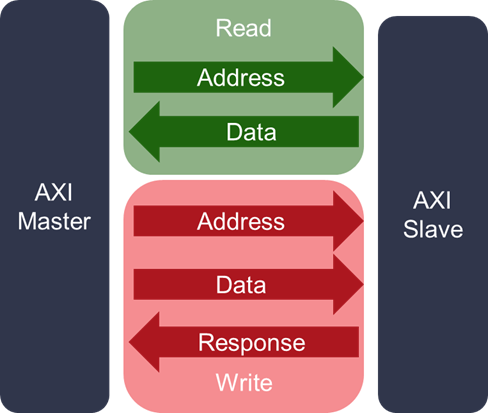

The AXI protocol defines 5 channels:

- 2 are used for Read transactions

- read address

- read data

- 3 are used for Write transactions

- write address

- write data

- write response

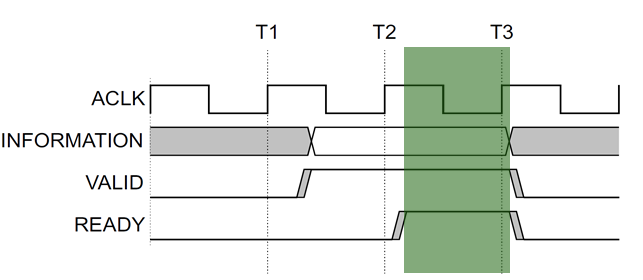

A channel is an independent collection of AXI signals associated with the VALID and READY signals.

Note: An AXI4/AXI3/AXI4-Lite Interface can be read only (only includes the 2 Read channels) or write only (only includes the 3 Write channels).

A piece of data transmitted on a single channel is called a transfer. A transfer happens when both the VALID and READY signal are high while there is a rising edge of the clock. For example, in the figure below, the transfer is happening on T3:

AXI Read Transactions

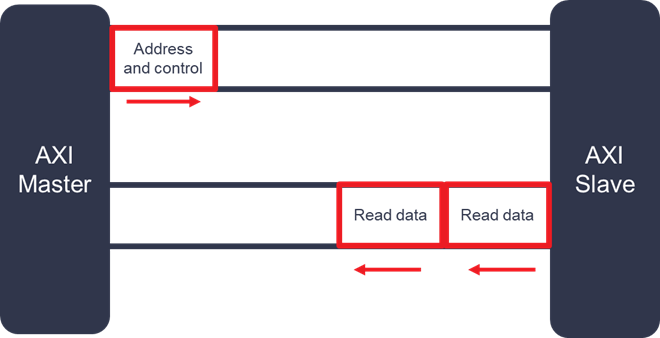

An AXI Read transactions requires multiple transfers on the 2 Read channels.

- First, the Address Read Channel is sent from the Master to the Slave to set the address and some control signals.

- Then the data for this address is transmitted from the Slave to the Master on the Read data channel.

Note that, as per the figure below, there can be multiple data transfers per address. This type of transaction is called a burst.

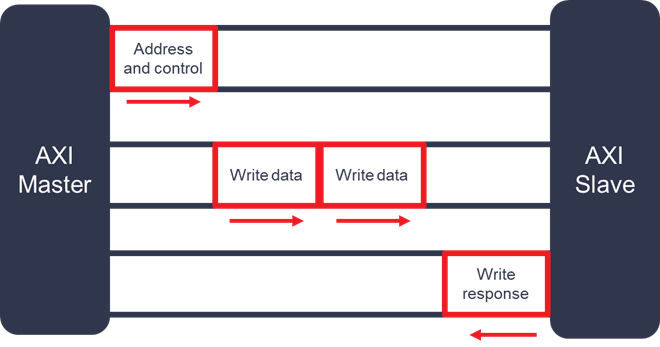

AXI Write Transactions

An AXI Write transactions requires multiple transfers on the 3 Read channels.

- First, the Address Write Channel is sent Master to the Slave to set the address and some control signals.

- Then the data for this address is transmitted Master to the Slave on the Write data channel.

- Finally the write response is sent from the Slave to the Master on the Write Response Channel to indicate if the transfer was successful.

The possible response values on the Write Response Channel are:

- OKAY (0b00): Normal access success. Indicates that a normal access has been successful

- EXOKAY (0b01): Exclusive access okay.

- SLVERR (0b10): Slave error. The slave was reached successfully but the slave wishes to return an error condition to the originating master (for example, data read not valid).

- DECERR (0b11): Decode error. Generated, typically by an interconnect component, to indicate that there is no slave at the transaction address

Note: Read transactions also have a response value but this response is transmitted as part of the Read Response Channel

AXI4 Interface requirements

There are some requirement documented in the AXI4 Specification.

The ones you absolutely want to remember are:

-

When a VALID (AxVALID/xVALID) signal is asserted, it must remain asserted until the rising clock edge after the slave asserts AxREADY/xREADY.

-

the VALID signal of the AXI interface sending information must not be dependent on the READY signal of the AXI interface receiving that information

- However, the state of the READY signal can depend on the VALID signal

-

A write response must always follow the last write transfer in the write transaction of which it is a part

-

Read data must always follow the address to which the data relates

-

A slave must wait for both ARVALID and ARREADY to be asserted before it asserts RVALID to indicate that valid data is available

In the next article of the AXI Basics Series we will simulate AXI4 Interfaces using the AXI Verification IP (AXI VIP).

Additional Learning

If you want to learn more about AXI, please see the other tutorials in this series:

https://support.xilinx.com/s/topic/0TO2E000000YNxCWAW/axi-basics-series?tabset-50c42=2